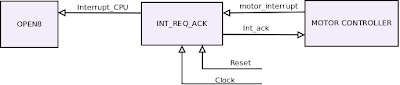

MOTOR CONTROLLER TO OPEN8 INTERRUPT INTERFACE

The Interrupt from the motor controller to the CPU needs to be high for 1 clock cycle. There is not interrupt acknowledge signal from the Open8 CPU that can turn off the interrupt after 1 clock signal. If the motor controller interrupt is more than one clock cycle, The CPU interprets it as a separate request. So there is a need for a moderator that

- Receives an interrupt request from the motor controller

- Responds to the interrupt by sending a signal to the CPU interrupt line which is high for exactly one clock cycle.

- After sending the interrupt request to the CPU, sends an interrupt acknowledge signal to the motor controller.

This moderator is Int_req_ack module.

The Int_req_ack module has a 2 bit counter which is initialized to “00”. When the motor interrupt goes high, the counter is incremented by 1 every clock cycle and the interrupt_CPU line goes high. Since we need the interrupt_CPU line to be high for exactly one clock signal, the counter is reset when it reaches “01”. When the counter value goes to “01”, the interrupt_CPU line goes low and an acknowledge signal (int_ack) is sent to the motor controller. The int_ack signal to the motor controller, pulls down the motor_interrupt signal. This is sensed by the int_req_ack module and resets the counter to “00”.

(a 1 bit counter would have sufficed. Made it two bits so that additional functionalities can be added if required)

--

Abishek Ramdas

NYU Poly

It's a good thought about a Motor controller. I have read your post and get some information about how it works and all that things.

ReplyDeleteMotor controller