Synthesis of the Motor Controller

The Flow of Asic design is

1. RTL Description

2. Simulation and testing of functionality

3. Synthesis of netlist using RTL Compiler

4. Verification of resultant netlist

The HDL Description of the motor controller is available. The next step is to synthesize it to a netlist made up of the standard cells.

The library used is the osu025_stdcells.lib

The HDL files for the motor controller are read by the RTL Compiler. The following lines are added to a tcl file which is then sourced from the RTL Compiler

File : rtl.tcl

set_attribute lib_search_path /path_to/cadence/local/osu_soc_v2.7/cadence/lib/tsmc025/signalstorm

read_hdl -vhdl ../HDL/motor_controller.vhd (location of motor controller)

elaborate

synthesize -to_mapped

write -mapped > motor_controller.v

write_script > script

This script was edited and sourced in the RTL compiler to synthesize the motor controller for verification. Note: no optimization parameters are specified.

as you can see the synthesis should succeed without errors. The resultant netlist is available in motor_controller.v. The next step is verification of the functionality of the netlist. This is done by porting the netlist to a schematic version in spectre and simulation using analog environment.

The netlist is imported to encounter and after generating a placed and routed layout without violations, it is saved as a gds2 file. The detailed procedure is given HERE

The GDS2 is ported into ICFB using a script provided by cadence and the schematic view is generated.

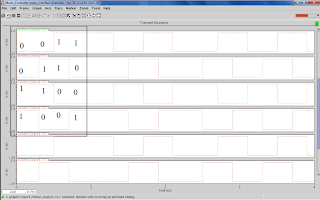

The schematic is simulated using the analog environment for verifying the netlist. The method of simulation done was load a control word into the motor controller and see the output. The control word loaded is 00110011 which means both the motors are moved forward by 3 steps, The waveforms are as follows

It can be seen that indeed both the motors shift in the right direction for 3 steps after which the control word is again loaded in by the user. The netlist is verified to be functionally correct. But the LVS do not match.

One main reason DRC fails is because of presence of labels for pins. Deleting the labels for the pins removed all DRC errors. LVS still failed to match. Was not able to look into the reasons for the want of time.

Abishek Ramdas

NYU Poly

1. RTL Description

2. Simulation and testing of functionality

3. Synthesis of netlist using RTL Compiler

4. Verification of resultant netlist

The HDL Description of the motor controller is available. The next step is to synthesize it to a netlist made up of the standard cells.

The library used is the osu025_stdcells.lib

The HDL files for the motor controller are read by the RTL Compiler. The following lines are added to a tcl file which is then sourced from the RTL Compiler

File : rtl.tcl

set_attribute lib_search_path /path_to/cadence/local/osu_soc_v2.7/cadence/lib/tsmc025/signalstorm

read_hdl -vhdl ../HDL/motor_controller.vhd (location of motor controller)

elaborate

synthesize -to_mapped

write -mapped > motor_controller.v

write_script > script

This script was edited and sourced in the RTL compiler to synthesize the motor controller for verification. Note: no optimization parameters are specified.

as you can see the synthesis should succeed without errors. The resultant netlist is available in motor_controller.v. The next step is verification of the functionality of the netlist. This is done by porting the netlist to a schematic version in spectre and simulation using analog environment.

The netlist is imported to encounter and after generating a placed and routed layout without violations, it is saved as a gds2 file. The detailed procedure is given HERE

The GDS2 is ported into ICFB using a script provided by cadence and the schematic view is generated.

The schematic is simulated using the analog environment for verifying the netlist. The method of simulation done was load a control word into the motor controller and see the output. The control word loaded is 00110011 which means both the motors are moved forward by 3 steps, The waveforms are as follows

It can be seen that indeed both the motors shift in the right direction for 3 steps after which the control word is again loaded in by the user. The netlist is verified to be functionally correct. But the LVS do not match.

One main reason DRC fails is because of presence of labels for pins. Deleting the labels for the pins removed all DRC errors. LVS still failed to match. Was not able to look into the reasons for the want of time.

Abishek Ramdas

NYU Poly

Comments

Post a Comment