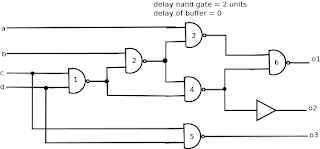

Levelization of circuits

Hello , When working with benchmark circuits, it is convenient to levelize the gates and work with levels. This is useful when you want to calculate some metric for all gates or wires. It is efficient than recursively traversing through all wires, gates, and fanouts. Here I upload a program that levelizes the iscas bench marks. It is written in perl. Use it the way you see fit and edit it if you find mistakes. Levelization 1. Assign level number 0 to all primary inputs 2. For each PI fanout Label that circuit line with level number of the PI Queue the logic gate driven by that fanout line (I need a queue) 3. While queue is not empty dequeue the next logic gate in the queue If all of the gate fanins are labeled with level numbers, then label the logic gate and its fanouts with maximum of input levels + 1. Queue all fanouts of the logic gate. Otherwise requeue the logic gate. Algorithm - Levelization loop inputlist - list of primary inputs